用于AI硬件加速器的基于電容器的架構

很多文章的報道都是由微觀而宏觀 , 今日小編講給大家帶來的關于用于AI硬件加速器的基于電容器的架構的資訊也不例外,希翼可以在一定的程度上開闊你們的視野!y有對用于AI硬件加速器的基于電容器的架構這篇文章感興趣的小伙伴可以一起來看看

IBM通過基于電容器的交叉點陣列用于模擬神經網絡 , 超越了數字技術 , 在深度學習計算中顯示出潛在的數量級改進 。模擬計算架構利用某些存儲設備的存儲能力和物理屬性 , 不僅用于存儲信息,而且還用于執行計算 。這有可能極大地減少計算機所需的時間和能源,因為不需要在內存和處理器之間穿梭數據 。缺點可能是計算精度降低,但是對于不需要高精度的系統,這是正確的權衡 。

【用于AI硬件加速器的基于電容器的架構】

在模擬神經網絡(NN)中,基于非易失性存儲器(NVM)的交叉點陣列已在推理任務方面取得了可喜的成果 。然而,對于NVM設備而言 , 難以對NN進行高精度訓練,因為成功的訓練取決于保持NN 權重的增量變化較小(需要大約1,000個更新狀態)和對稱(以便使正負更新平均平衡) 。這些問題可以通過使用電容器來解決 。如果電子數量多,由于可以延續增加或減少電荷,因此可以實現模擬和對稱分量更新 。我們在2018年VLSI技術研討會上提出了一種用于模擬神經網絡的基于電容器的交叉點陣列 。新的架構實現了分量更新的對稱性和線性記錄 。

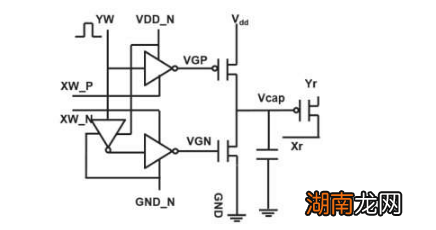

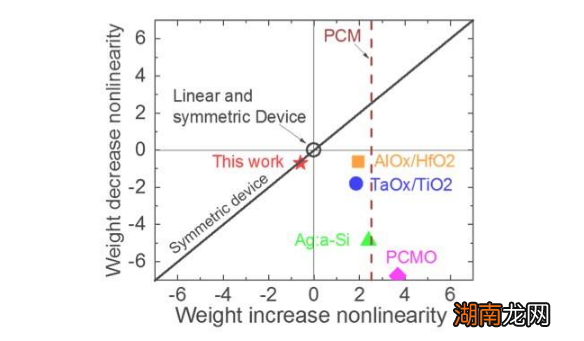

圖1顯示了基于電容器的交叉點陣列的單位單元示意圖 。關鍵組件是連接到讀出場效應晶體管(FET)的電容器 。電容器上的電荷代表突觸權重,電容器通過兩個電流源FET充電和放電 。圖2分別顯示了十個周期的400個正更新,然后是400個負更新,分別測量了一個單元的讀出FET的電導變化和相應的電容器電壓 。圖3比較了基于電容器的模擬突觸與其他NVM技術的實驗非線性更新因子 。基于電容器的單元電池提供了迄今為止證明的最佳對稱性和線性 。圖4演示了在2×2陣列上的并行權重更新 。

即使電容器易失,也可以在分量更新過程中補償泄漏 。由于訓練反復進行前,后和權重更新循環 , 因此前一個循環衰減后的權重將用于下一個循環的訓練并得到更新 。因此,不需要故意的刷新周期 。我們使用完全連接的網絡測試了保留時間對訓練的影響 。它具有一個輸入層,兩個隱藏層和一個輸出層(圖5),并通過隨機梯度下降和反向傳播在MNIST數據集上進行了訓練 。假設每層的訓練周期長度(向前+向后+更新)為200 ns,并且突觸權重隨RC時間常數τ衰減,我們發現當τ> 106×訓練周期時 , 電容器電荷損耗對訓練精度的影響可以忽略不計長度(圖6) 。我們還測試了卷積網絡的保留時間要求 。我們的測試網絡有兩個卷積層,兩個卷積層和兩個完全連接的層(圖7) 。由于卷積層中的分量分配(重用),因此對于卷積層的保留要求卷積神經網絡(CNN)大約大600(圖8) 。

對于完全連接的和卷積神經網絡,我們估量了這種基于電容器的陣列的可擴展性與泄漏的函數關系(圖9) 。圓形數據點表明,電容器隨傳輸晶體管泄漏呈線性比例變化 。方形數據點表明,當泄漏較大時,電池面積由電容器決定;當泄漏電流較小時,該區域將由單元中的FET支配 。對于具有1 fA /單元泄漏的DRAM技術,對于完全連接的神經網絡,電容器<1fF /單元需要電容器,而CNN則需要?100 fF /單元 。對于更大的輸入和更多層的可伸縮性需要進一步研究 。即使在輸入變大時可能需要更大的電容器,我們的初步結果(將要公布)表明該網絡/算法優化可以減少電容器需求 。

IBM現在正在研究具有優化模擬行為的新型理想內存 。由于已有技術和工藝可用,這些電容器將同意 加快模擬AI內核的實現 。

除了我們的電容器方法外,IBM正在探究用于模擬存儲器和計算的其他新穎元件,例如相變存儲器(PCM)和電阻式RAM(RRAM) 。這些元素在細胞面積,保留 , 對稱性和成熟度方面有所不同 。模擬加速器是IBM Research AI的AI硬件加速器產品線的一個組成部分 。開辟流程首先要從現有的GPU加速器中獲得最大收益,然后是利用近似計算的創新數字AI內核 。

猜你喜歡

- 黃色表情 黃色表示禁止停止用于禁止標志

- Plannuh籌集了400萬美元 用于擴展AI驅動的營銷

- ?Method360啟動數據管理加速器

- 主要用于低排量汽車嗎 92號汽油適用于什么車

- Tobii的眼動追蹤I系列具有第二個用于面對面交流的屏幕

- 蘋果手機硬件檢測 蘋果手機硬件檢測app

- 谷歌發布了全新的谷歌Pixel 3a/3a XL以及一系列全新的軟硬件

- 超敏感設備用于回收原子

- 新型晶體將電子限制在一維空間 可用于開發自旋電子器件

- Ezoic籌集了3300萬美元用于優化人工智能網站